Consumo energetico nell’elettronica: uno studio dell’Ateneo friulano per migliorarne l’efficienza

L’articolo, pubblicato sulla rivista scientifica “Nature Electronics”, è frutto della sinergia gruppo di nanoelettronica dell’università di Udine con il MIT di Boston

David Esseni: “Gli effetti di confinamento e trasporto quantistico nei transistori a nanofilo sono sfruttati per ridurre le tensioni e quindi l’energia di funzionamento”

L’ingente consumo energetico delle tecnologie dell’informazione è talvolta sottovalutato rispetto al consumo di altri settori industriali. Tuttavia, le tecnologie dell’informazione consumano già oggi una frazione consistente del fabbisogno globale di energia, e le proiezioni indicano che questa frazione è inesorabilmente destinata ad aumentare, anche a causa dell’esplosione delle applicazioni di intelligenza artificiale. Per questo motivo, la riduzione del consumo energetico delle tecnologie dell’informazione attraverso transistori innovativi è l’obiettivo di un’ampia comunità tecnico-scientifica, che vede impegnato anche l’Ateneo di Udine.

Un importante risultato è stato raggiunto grazie all’articolo pubblicato sulla prestigiosa rivista Nature Electronics dal titolo Realizing the potential of ultra-scaled tunneling electronics through extreme quantum confinement, frutto di una collaborazione tra il gruppo di nanoelettronica dell’università di Udine (https://nanoelectronics.uniud.it/) e i ricercatori del MIT di Boston. Per l’Ateneo di Udine hanno contribuito i professori David Esseni e Marco Pala.

“I transistori al silicio, utilizzati per amplificare e commutare i segnali, sono un componente fondamentale della maggior parte dei dispositivi elettronici, dagli smartphone alle automobili – spiega David Esseni -. Ma la tecnologia dei semiconduttori al silicio è frenata da un limite fisico fondamentale alla riduzione della tensione di alimentazione dei circuiti integrati e quindi dell’energia dissipata. Questo limite, noto come “tirannia di Boltzmann”, ostacola l’efficienza energetica dei computer e di tutto il comparto delle tecnologie dell’informazione”.

Marco Pala e David Esseni

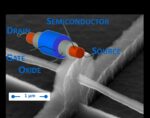

Nel tentativo di superare questo limite fondamentale, i ricercatori del MIT hanno fabbricato un diverso tipo di transistore tridimensionale utilizzando un insieme unico di materiali semiconduttori ultrasottili. I dispositivi, costituiti da nanofili verticali larghi solo pochi nanometri, sono in grado di fornire prestazioni paragonabili a quelle dei transistori al silicio di ultima generazione, pur a tensioni molto più basse rispetto ai dispositivi convenzionali. Il gruppo di nanoelettronica di Udine ha svolto simulazioni di trasporto quantistico per i transistori a nanofilo, che hanno contribuito a comprendere e ottimizzare il funzionamento di questi sofisticati ed innovativi dispositivi nanoelettronici.

“Questi nuovi transistori – spiga ancora Esseni – sfruttano effetti di meccanica quantistica per ottenere contemporaneamente un funzionamento a bassa tensione e con prestazioni elevate in un’area di pochi nanometri quadrati. Le dimensioni estremamente ridotte dei transistori consentiranno di impacchettare un numero maggiore di transistori 3D in un chip per computer, ottenendo così un’elettronica veloce e potente, ma anche più efficiente dal punto di vista energetico. Ci sono ancora molte sfide da superare per rendere questi dispositivi idonei per una tecnologia industriale, ma i risultati pubblicati in Nature Electronics rappresentano una svolta nella prova di fattibilità di transistori che sfruttano proficuamente effetti di meccanica quantistica per migliorare le prestazioni energetiche”.

Il gruppo di nanoelettronica dell’Università di Udine lavora da 15 anni sui dispositivi e circuiti elettronici per alta efficienza energetica, nel contesto di numerose collaborazioni nazionali ed internazionali con istituti di ricerca e industrie ad alta tecnologia. Queste ricerche sono state supportate da diversi progetti finanziati dalla Unione Europea o dal MUR italiano. Attualmente, ad esempio, il gruppo di nanoelettronica è impegnato nel progetto “Dirac cold-source transistor technologies towards attojoule switching” finanziato dal programma Horizon Europe, e nel progetto PRIN 2022 “Ferroelectric Neuromorphic Learning for Tactile Edge Application”, coordinato dal Prof. David Esseni e finanziato dal MUR.

Foto anteprima: Un transistore e nanofilo. Foto al microscopio elettronico (toni di grigio) e disegno della struttura utilizzato come punto di partenza per la simulazione